- •Методические указания

- •1. Цель и практическое содержание методических указаний

- •2.2. Регистры и стек 32-разрядных процессоров Регистры

- •Регистры общего назначения

- •2.3. Организация памяти

- •Типы адресов

- •Режимы адресации

- •2.4. Прерывания и исключения

- •2.5. Основные понятия Защищенного режима работы процессора

- •2.6. Механизмы страничной переадресации

- •Базовый механизм страничной переадресации.

- •Режим pse

- •Режим pae.

- •2.7. Примеры команд 32-разрядного процессора

- •3. Задание на выполнение работы

- •Варианты задания

- •4. Содержание отчета по курсовой работе

- •5. Оформление пояснительной записки

2.3. Организация памяти

Пространство памяти (MemorySpace) предназначено для хранения кодов инструкций и данных, для доступа к которым имеется богатый выбор способов адресации. Память для процессоров представляется в виде линейной последовательности байт.

Память для 32-разрядных процессоров 80х86 подразделяется на байты(8 бит),слова(16 бит),двойные слова (32 бит) иучетверенные слова(64 бит). Все пространство памяти разбивается напараграфы– области из 16 смежных байт, начиная с нулевого адреса.

Более крупными единицами организации памяти являются страницы и сегменты. Сегмент– это блок пространства памяти определенного назначения. К элементам сегмента возможно обращение с помощью различных инструкций процессора, использующих разные режимы адресации для формирования адреса в пределах сегмента. Максимальный размер сегмента - 4 Гбайт.

Память может логически организовываться в виде одного или множества сегментов переменной длины. Кроме сегментации, в защищенном режиме возможно разбиение (Paging) логической памяти на страницы размером 4 Кбайт, каждая из которых может отображаться на любую область физической памяти. Начиная с 5-го поколения процессоров, появилась возможность увеличения размера страницы до 4 Мбайт.

Сегментация и разбиение на страницы могут применяться в любых сочетаниях. Сегментация является средством организации логической памяти на прикладном уровне. Разбиение на страницы применяется на системном уровне для управления физической памятью. Сегменты и страницы могут выгружаться из физической оперативной памяти на диск и по мере необходимости подкачиваться с него обратно в физическую память. Таким образом реализуется виртуальная память.

Типы адресов

Применительно к памяти различают три адресных пространства: логическое, линейное и физическое. Основным режимом работы 32-разрядных процессоров считается защищенный режим, в котором работают все механизмы преобразования адресных пространств.

Логический адрес,также называемый виртуальным, состоит из селектора сегмента и эффективного адреса, называемого также смещением (offset). Селектор сегмента хранится в старших 14 битах сегментного регистра (CS[0:15],DS[0:15],ES[0:15],SS[0:15],FS[0:15] илиGS[0:15]), участвующего в адресации конкретного элемента памяти. По значению селектора из специальных таблиц, хранящихся в памяти, извлекается начальный адрес сегмента.

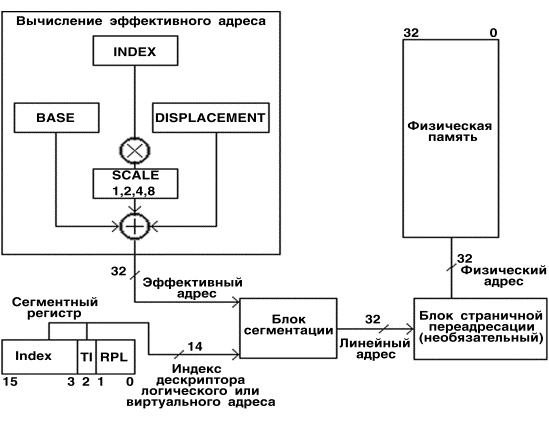

Эффективный адресформируется суммированием компонентbase,index,displacementс учетом масштабаscale(см. 2.2). Поскольку каждая задача может иметь до 16 Кбайт селекторов (214), а смещение, ограниченное размером сегмента, может достигать 4 Гбайт, логическое адресное пространство для каждой задачи может достигать 64 Тбайт. Все это пространство виртуальной памяти в принципе доступно программисту (при условии поддержки со стороны операционной системы).

Блок сегментации транслирует логическое адресное пространство в 32-битное пространство линейных адресов. Линейный адресобразуется сложением базового адреса сегмента с эффективным адресом. Базовый адрес сегмента в реальном режиме образуется умножением содержимого используемого сегментного регистра на 16 (как и в 8086). В защищенном режиме базовый адрес загружается из дескриптора, хранящегося в таблицеGDT(см. раздел 4), по селектору, загруженному в используемый сегментный регистр.

32-разрядный физический адреспамяти образуется после преобразования линейного адреса блоком страничной переадресации. Он выводится на внешнюю шину адреса процессора. В простейшем случае (при отключенном блоке страничной переадресации) физический адрес совпадает с линейным (рис. 1).

Рис. 1. Формирование адреса памяти 32-разрядных процессоров в защищенном режиме.

Включенный блок страничной переадресации осуществляет трансляцию линейного адреса в физический страницами размером 4 Кбайт (для старших поколений процессоров также возможны страницы размером 2 или 4 Мбайт). Блок обеспечивает расширение разрядности физического адреса процессоров шестого поколения до 36 бит. Блок переадресации может включаться только в защищенном режиме.