- •Table of Contents

- •List of Illustrations

- •List of Tables

- •2.1 Programmer's Model

- •2.1.2 Supervisor Programmer's Model

- •2.1.3 Status Register

- •2.2 Data Types and Addressing Modes

- •2.3 Data Organization in Registers

- •2.3.1 Data Registers

- •2.3.2 Address Registers

- •2.4 Data Organization in Memory

- •2.5 Instruction Set Summary

- •3.1 Address Bus

- •3.2 Data Bus

- •3.3 Asynchronous Bus Control

- •3.4 Bus Arbitration Control

- •3.6 System Control

- •3.7 M6800 Peripheral Control

- •3.11 Signal Summary

- •4.1 Data Transfer Operations

- •4.1.1 Read Cycle

- •4.1.2 Write Cycle

- •4.2 Other Bus Operations

- •5.1 Data Transfer Operations

- •5.1.1 Read Cycle

- •5.1.2 Write Cycle

- •5.1.4 CPU Space Cycle

- •5.2 Bus Arbitration

- •5.2.1 Requesting the Bus

- •5.2.2 Receiving the Bus Grant

- •5.3 Bus Arbitration Control

- •5.4 Bus Error and Halt Operation

- •5.4.1 Bus Error Operation

- •5.4.2 Retrying the Bus Cycle

- •5.4.4 Double Bus Fault

- •5.5 Reset Operation

- •5.7 Asynchronous Operation

- •5.8 Synchronous Operation

- •6.1 Privilege Modes

- •6.1.1 Supervisor Mode

- •6.1.2 User Mode

- •6.1.3 Privilege Mode Changes

- •6.1.4 Reference Classification

- •6.2 Exception Processing

- •6.2.1 Exception Vectors

- •6.2.2 Kinds of Exceptions

- •6.2.3 Multiple Exceptions

- •6.2.4 Exception Stack Frames

- •6.2.5 Exception Processing Sequence

- •6.3 Processing of Specific Exceptions

- •6.3.1 Reset

- •6.3.2 Interrupts

- •6.3.3 Uninitialized Interrupt

- •6.3.4 Spurious Interrupt

- •6.3.5 Instruction Traps

- •6.3.6 Illegal and Unimplemented Instructions

- •6.3.7 Privilege Violations

- •6.3.8 Tracing

- •6.3.9 Bus Error

- •6.3.10 Address Error

- •7.1 Operand Effective Address Calculation Times

- •7.2 Move Instruction Execution Times

- •7.3 Standard Instruction Execution Times

- •7.4 Immediate Instruction Execution Times

- •7.5 Single Operand Instruction Execution Times

- •7.6 Shift/Rotate Instruction Execution Times

- •7.7 Bit Manipulation Instruction Execution Times

- •7.8 Conditional Instruction Execution Times

- •7.9 JMP, JSR, LEA, PEA, and MOVEM Instruction Execution Times

- •7.10 Multiprecision Instruction Execution Times

- •7.11 Miscellaneous Instruction Execution Times

- •7.12 Exception Processing Execution Times

- •8.1 Operand Effective Address Calculation Times

- •8.2 Move Instruction Execution Times

- •8.3 Standard Instruction Execution Times

- •8.4 Immediate Instruction Execution Times

- •8.5 Single Operand Instruction Execution Times

- •8.6 Shift/Rotate Instruction Execution Times

- •8.7 Bit Manipulation Instruction Execution Times

- •8.8 Conditional Instruction Execution Times

- •8.9 JMP, JSR, LEA, PEA, and MOVEM Instruction Execution Times

- •8.10 Multiprecision Instruction Execution Times

- •8.11 Miscellaneous Instruction Execution Times

- •8.12 Exception Processing Execution Times

- •9.1 Operand Effective Address Calculation Times

- •9.2 Move Instruction Execution Times

- •9.3 Standard Instruction Execution Times

- •9.4 Immediate Instruction Execution Times

- •9.5 Single Operand Instruction Execution Times

- •9.6 Shift/Rotate Instruction Execution Times

- •9.7 Bit Manipulation Instruction Execution Times

- •9.8 Conditional Instruction Execution Times

- •9.10 Multiprecision Instruction Execution Times

- •9.11 Miscellaneous Instruction Execution Times

- •9.12 Exception Processing Execution Times

- •10.1 Maximum Ratings

- •10.2 Thermal Characteristics

- •10.3 Power Considerations

- •10.4 CMOS Considerations

- •10.5 AC Electrical Specification Definitions

- •10.6 MC68000/68008/68010 DC Electrical Characteristics

- •10.7 DC Electrical Characteristics

- •10.13 MC68EC000 DC Electrical Specifications

- •11.1 Pin Assignments

- •11.2 Package Dimensions

STATE 12 The write portion of the cycle starts in S12. The valid function codes on

FC2–FC0, the address bus lines, AS, and R/W remain unaltered.

STATE 13 During S13, no bus signals are altered.

STATE 14 On the rising edge of S14, the processor drives R/W low.

STATE 15 During S15, the data bus is driven out of the high-impedance state as the data to be written are placed on the bus.

STATE 16 At the rising edge of S16, the processor asserts U D S or L D S . The processor waits for DTACK or BERR or VPA, an M6800 peripheral signal. When VPA is asserted during S16, the cycle becomes a peripheral cycle (refer to Appendix B M6800 Peripheral Interface). If neither termination signal is asserted before the falling edge at the close of S16, the processor inserts wait states (full clock cycles) until either DTACK or BERR is asserted.

STATE 17 During S17, no bus signals are altered.

STATE 18 During S18, no bus signals are altered.

STATE 19 On the falling edge of the clock entering S19, the processor negates AS, UDS, and LDS. As the clock rises at the end of S19, the processor places the address and data buses in the high-impedance state, and drives R/W high. The device negates DTACK or BERR at this time.

5.1.4 CPU Space Cycle

A CPU space cycle, indicated when the function codes are all high, is a special processor cycle. Bits A16–A19 of the address bus identify eight types of CPU space cycles. Only the interrupt acknowledge cycle, in which A16–A19 are high, applies to all the microprocessors described in this manual. The MC68010 defines an additional type of CPU space cycle, the breakpoint acknowledge cycle, in which A16–A19 are all low. Other configurations of A16–A19 are reserved by Motorola to define other types of CPU cycles used in other M68000 Family microprocessors. Figure 5-10 shows the encoding of CPU space addresses.

|

FUNCTION |

|

|

|

|

|

|

|

|

|

|

|

ADDRESS BUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

2 |

CODE |

0 |

|

31 |

|

|

|

|

|

|

|

23 |

|

|

|

19 |

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

BREAKPOINT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ACKNOWLEDGE |

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(MC68010 only) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTERRUPT |

|

|

|

|

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

LEVEL |

1 |

|||

ACKNOWLEDGE |

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPU SPACE

TYPE FIELD

Figure 5-10. CPU Space Address Encoding

MOTOROLA |

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL |

5-9 |

The interrupt acknowledge cycle places the level of the interrupt being acknowledged on address bits A3–A1 and drives all other address lines high. The interrupt acknowledge cycle reads a vector number when the interrupting device places a vector number on the data bus and asserts DTACK to acknowledge the cycle.

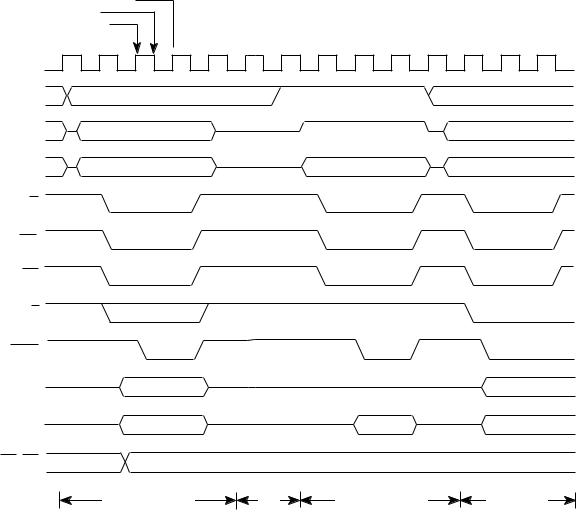

The timing diagram for an interrupt acknowledge cycle is shown in Figure 5-11.

Alternately, the interrupt acknowledge cycle can be autovectored. The interrupt acknowledge cycle is the same, except the interrupting device asserts VPA instead of DTACK. For an autovectored interrupt, the vector number used is $18 plus the interrupt level. This is generated internally by the microprocessor when VPA (or AVEC) is asserted on an interrupt acknowledge cycle. DTACK and V P A (AVEC) should never be simultaneously asserted.

IPL2–IPL0 VALID INTERNALLY

IPL2–IPL0 SAMPLED

IPL2–IPL0 TRANSITION

S0 S1 S2 S3 S4 S5 S6 S7 S0 S1 S2 S3 S4 S5 S6 S7 S0 S1 S2 S3 S4 w w w w S5 S6

S6 S7 S0 S1 S2 S3 S4 S5 S6 S7 S0 S1 S2 S3 S4 w w w w S5 S6

CLK

FC2–FC0

A23–A4

A3–A1

AS

UDS*

LDS

R/W

DTACK

D15–D8

D7–D0

IPL2–IPL0

LAST BUS CYCLE OF INSTRUCTION |

STACK |

IACK CYCLE |

STACK AND |

(READ OR WRITE) |

PCL |

(VECTOR NUMBER |

VECTOR |

|

(SSP) |

ACQUISITION) |

FETCH |

*Although a vector number is one byte, both data strobes are asserted due to the microcode used for exception processing. The processor does not recognize anything on data lines D8 through D15 at this time.

Figure 5-11. Interrupt Acknowledge Cycle Timing Diagram

5-10 |

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL |

MOTOROLA |