11

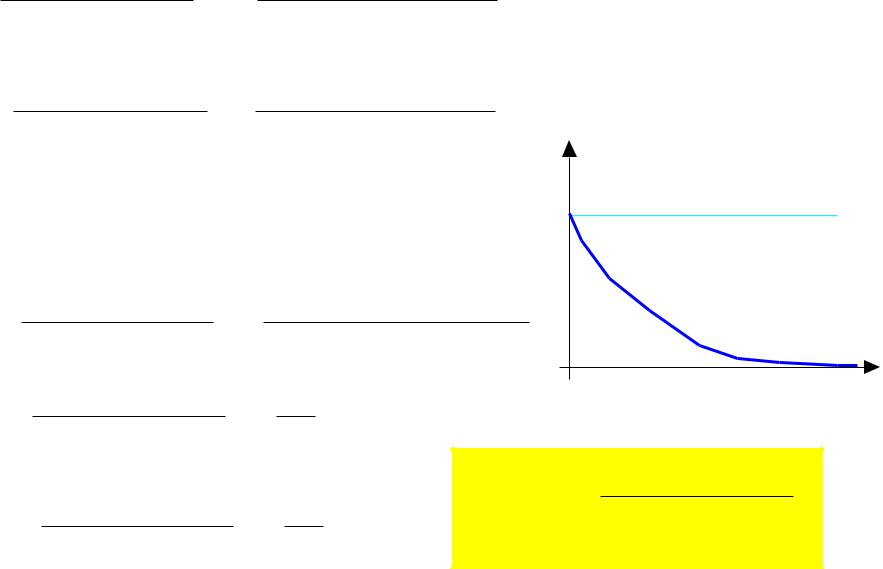

LOGIC “0” TRANSFER: |

Vin |

= 0 |

|

|

|

|

S |

|

|

|

|

|

|

D |

Vx |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

Assume at t = 0: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

MP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ID |

|

|

|

C |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

Vx (t = 0) = Vmax = VDD - VT,MP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CK = 0 -> VDD |

|

|

|

|

|

|

|

CK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VGS = VDD, VDS = Vmax = VDD - VT,MP |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDS £ VGS - VT,MP => nMOS in LIN |

||||||||||||||||||||||

- C |

|

dVx |

= |

kn |

(2(V - V |

)V - V2 ) |

|

|

|

|

|

|

NOTE VSB = 0 |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

x |

dt |

2 |

|

|

DD |

|

T,MP |

x |

x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

t |

= - |

2 Cx |

|

Vx |

|

|

|

|

|

dVx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

ò dt |

|

|

|

|

ò |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

kn |

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

0 |

|

|

|

|

VDD −VT,MP (2(VDD - VT,MP )Vx - Vx ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

t = |

|

|

|

2C |

|

|

|

|

|

é2(VDD - VT,MP )- Vx |

ùö |

|

V |

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

x |

|

|

|

lnê |

|

|

|

ú |VDD −VT , M P |

|

|

|

|

|

||||||||||||||||||

|

k (V - V |

|

) |

ç |

|

ë |

|

V |

|

|

÷ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

n |

|

DD |

T,MP è |

|

|

x |

|

|

û |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

ø |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

Kenneth R. Laker, University of Pennsylvania

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

t = |

|

2C |

x |

æ |

|

|

é2(VDD - VT,MP )- Vx |

ùö |

V |

|

||

|

|

|

|

lnê |

|

|

ú |

x |

|

||||

|

|

|

|

ç |

|

|

|VDD −VT , M P |

|

|||||

|

|

|

|

|

|

|

|

Vx |

|

÷ |

|

|

|

|

kn (VDD - VT,MP )è |

|

|

ë |

|

ø |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

û |

|

|

|

|

t = |

|

Cx |

|

|

|

é2(VDD - VT,MP )- Vx |

ù |

|

|

|||

|

kn (VDD - VT,MP ) |

lnê |

Vx |

|

ú |

V (t) |

|||||||

|

|

|

|

ë |

|

û |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

x |

|

|

|

Transfers a STRONG logic “0” |

|

Vmax |

VDD - VT,MP |

||||||||

|

|

|

|

||||||||||

|

tfall = t10% - t90% |

|

|

|

é(2 - 0.9)(VDD - VT,MP )ù |

|

|||||||

t |

90% = |

Cx |

|

|

|

|

|||||||

(VDD |

- VT,MP ) |

lnê |

0.9(VDD - VT,MP ) |

|

ú |

|

|||||||

|

|

kn |

|

ë |

|

û |

t |

||||||

|

|

|

|

Cx |

|

|

|

æ 1.1ö |

|

|

|

|

|

|

|

= kn (VDD - VT,MP )lnè 0.9ø |

|

|

|

Cx |

|||||||

|

|

|

|

|

|

|

|

|

|

tfall = 2.74 |

|||

|

t10% |

= |

|

Cx |

|

|

|

lnæ1.9ö |

(VDD - VT,MP ) |

||||

|

|

|

|

|

|

|

kn |

||||||

|

|

kn (VDD - VT,MP ) |

|

è 0.1ø |

|

|

|

|

|||||

Kenneth R. Laker, University of Pennsylvania

13

CK = 0: CHARGE STORAGE AND CHARGE LEAKAGE

At t = 0 CK = 0, Vx = Vmax, Vin = 0 V |

|

|

VDD |

|

|||||

|

M2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

V = 0 |

|

Vx |

|

|

M1 |

in |

|

|

|

|

|

MP |

Ileakage |

C |

I |

|

= 0 |

|

gate |

||||

|

|

x |

|

|

CK = 0 |

|

|

|

Vin = 0 |

|

VCK = 0 |

|

|

|||

|

|

|

|

Vout

Ileakage Vx

n |

+ |

Cx |

|

n+ |

|

|

|

Isubsthreshold |

p - Sub |

|

Ireverse |

|

|

|

|

|

Ileakage = Isubthreshold + Ireverse |

Kenneth R. Laker, University of Pennsylvania

14

Vin |

= 0 |

|

V = 0 |

Ileakage |

V |

||

|

|||||||

|

CK |

|

|

x |

|||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

n |

+ |

Cx |

Isubsthreshold |

n+ |

|

|

|

|

p - Sub |

Ireverse |

|

|

|

|

|

Ileakage = Isubthreshold + Ireverse |

|

|

Ileakage |

Vx |

Isubthreshold |

|

|

|

|

|

|

|

|

|

Cj |

|

|

Cin |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

||||||||||||

|

|

|

|

|

Ireverse |

Cin = Cgb + Cpoly + Cmetal |

||||||||

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Cx = Cin + Cj

DRAIN-SUB PN JUNCTION

Kenneth R. Laker, University of Pennsylvania

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ileakage |

V |

|

|

|

|

|

|

|

15 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cx = Cin + Cj |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cj |

|

|

|

|

|

|

C |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Isubthreshold |

|

|

|

|

|

|

|

|

|

|

|

Ireverse |

|

|

|

|

|

|

|

|

|

|

|

in |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cin = Cgb + Cpoly + Cmetal |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

dominant |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

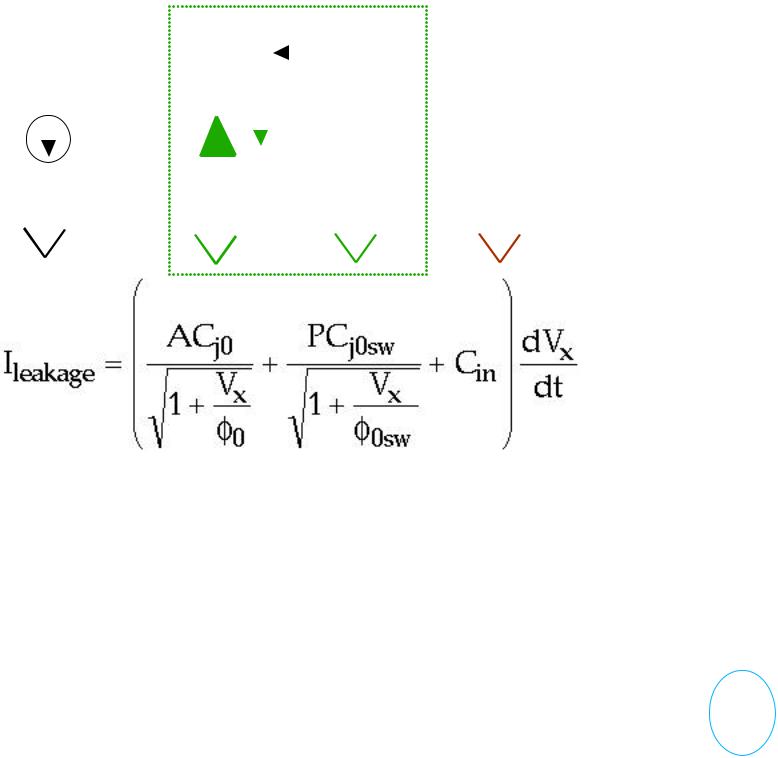

Ileakage = Isubthreshold + Ireverse |

||||||||||||

|

|

|

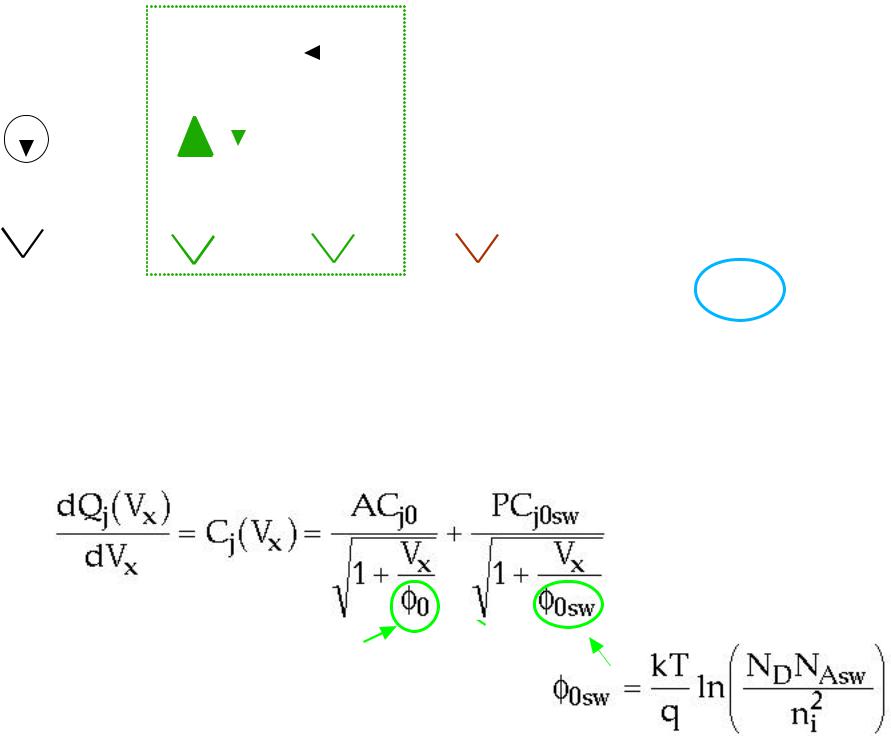

Q = Qj(Vx) + Qin = Qj(Vx) + CinVx |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

Ileakage |

= |

dQ |

= |

dQj (Vx ) |

|

+ |

dQin |

= |

dQj(Vx ) |

|

dVx |

+ C |

|

dVx |

|

|||||||||||||||||

|

|

|

dt |

|

|

|

dt |

|

|

dt |

|

|

in |

dt |

|||||||||||||||||||||

where |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

dVx dt |

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

f0 |

= |

kT |

N |

D |

N ö |

|||

|

lnç |

|

|

A |

÷ |

|||

q |

|

|

2 |

|

||||

|

|

è |

|

ni |

ø |

|||

Kenneth R. Laker, University of Pennsylvania

|

|

|

|

|

|

|

|

|

|

|

Ileakage |

V |

16 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

x |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Isubthreshold |

|

|

|

|

|

|

|

|

|

|

|

|

|

Cj |

|

|

|

|

|

|

Cin = Cgb + Cpoly + Cmetal |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

Ireverse |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ileakage = Isubthreshold + Ireverse |

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Solve to estimate the actual charge leakage

FOR QUICK EXTIMATE OF WORST CASE LEAKAGE BEHAVIOR

Cx,min = Cgb + Cpoly + Cmetal + Cj,min

Cj,min -> min Cj obtained when Vx = Vmax

worst case hold time (thold) -> shortest time for Vx to drop from its initial logic “1” value to Vth due to leakage.

thold |

= |

Qcritical,min |

where D Qcritical,min |

= Cx,min |

|

Vmax |

- |

VDD ö |

|

|

|

|

|

|

è |

|

|

|

ø |

|

|

|

|

|

|

|

2 |

||

|

|

Ileakage,max |

|

|

|

|

|||

Kenneth R. Laker, University of Pennsylvania |

Vth |

|

17

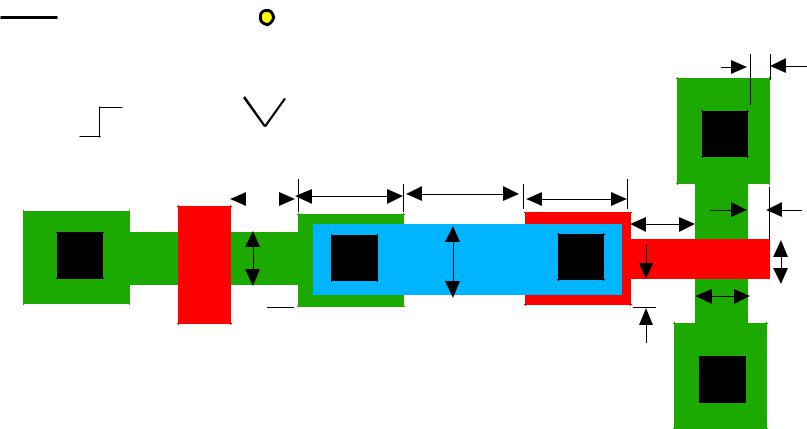

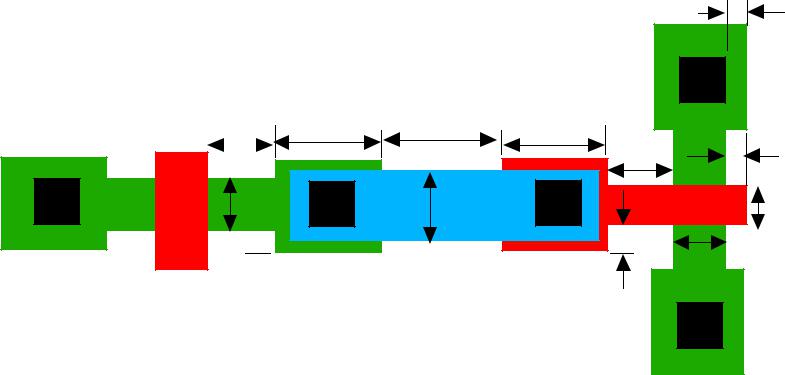

EXAMPLE 9.2

Consider the soft-node structure shown, which consists of the drain (or source depending on current direction) terminal of the pass transistor, connected to the poly gate of an nMOS driver transisitor via a metal interconnect. Estimate the worst-case holding time if VDD = 5 V and the soft-node is initially charged to Vmax.

MP |

|

Vx |

|

|

|

|

M1 |

|||||||

|

||||||||||||||

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1μ |

|

|

|

|

|

|

|

|

Cx |

|

|||||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CK

3μ |

6μ |

5μ |

6μ |

3μ |

1μ |

|

|

|

|

||

4μ |

|

5μ |

|

2μ |

2μ |

1μ |

|

|

|

4μ |

|

|

|

poly |

|

||

diffusionmetal |

|

||||

CK

Kenneth R. Laker, University of Pennsylvania

VT0 = 0.8 V |

|

|

|

|

|

C |

|

= 0.065 fF/μm2 |

|

|

18 |

|||||||||||

|

|

|

|

|

ox |

|

|

|

||||||||||||||

γ = 0.4 V1/2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

C’metal = 0.036 fF/μm2 |

|

|

|

||||||||||||||

|2φF| = 0.6 V |

|

|

|

|

C’poly = 0.055 fF/μm2 |

|

1μ |

|||||||||||||||

φ0 = 0.88 V |

|

|

|

|

|

|

C |

j0 |

= 0.095 fF/μm2 |

|

|

|

|

|||||||||

φ0sw = 0.95 V |

|

|

|

|

C |

|

= 0.2 fF/μm |

|

|

|

|

|||||||||||

|

|

|

|

j0sw |

|

|

|

|

||||||||||||||

Ileakage,max = 0.85 pA |

|

|

|

|

|

|

|

|||||||||||||||

|

|

3μ |

6μ |

5μ |

6μ |

3μ |

1μ |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4μ |

5μ |

|

2μ |

2μ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1μ |

diffusionmetal |

|

4μ |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

poly |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CK |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

C = C |

ox |

W L |

mask |

= 0.065 fF/μm2 (4 μm x 2 μm) = 0.52 fF |

|

|||||||||||||||||

gb |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

C |

= C’ |

metal |

|

W L |

metal |

= 0.036 fF/μm2 (5 μm x 5 μm) = 0.90 fF |

||||||||||||||||

metal |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

C |

= C’ |

poly |

W L |

poly |

= 0.055 fF/μm2 (36 μm2 + 6 μm2 + 2 μm2) = 2.42 fF |

|||||||||||||||||

poly |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

C |

|

= C |

A |

|

|

= 0.095 fF/μm2 (36 μm2 + 12 μm2) = 4.56 fF |

||||||||||||||||

bottom |

|

|

|

|

j0 |

|

|

bottom |

|

|

|

|

|

|

|

|

|

|

|

|||

Csidewall = Cj0swPsidewall = 0.2 fF/μm (30 μm) = 6.00 fF |

|

|

||||||||||||||||||||

Kenneth R. Laker, University of Pennsylvania

Need Vmax to determine Cj,min |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|||||||||||||||||||

|

|

V = V − V − γ |

|

|

|

|

|

|

|

|

|

− |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

( |

|2φ |+ V |

|2φ | |

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

max |

|

DD |

|

|

T0,MP |

|

|

|

|

|

|

|

F |

|

max |

|

|

|

|

|

|

F ) |

|

||||||||||||||||

|

|

|

|

= 5.0V− 0.8V− 0.4V1/2 ( |

|

|

|

|

|

|

− |

|

|

|

|

|

|

) |

||||||||||||||||||||||||

|

|

|

0.6V+ Vmax |

|

0.6V |

|||||||||||||||||||||||||||||||||||||

Solving for Vmax: Vmax = 3.68 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

CC |

|

= |

|

|

Cbottom |

|

|

+ |

|

Csidewall |

|

|

= |

|

4.56fF |

|

|

+ |

|

6.00fF |

= 4.71 fF |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

db, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

j,min |

|

|

|

|

Vx,max |

|

|

|

|

|

Vx,max |

|

|

|

|

3.68 |

|

|

|

|

|

|

|

|

|

3.68 |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

1 + |

|

|

|

|

1 + |

|

|

|

|

|

|

|

|

1 + |

|

|

|

|

|

|

1 + |

|

|

|

|

|

|

|

|||||||||||

|

|

|

f0 |

|

|

|

|

|

f0 s w |

|

|

|

|

0.88 |

|

|

|

|

|

|

0.95 |

|

|

|

||||||||||||||||||

Cx,min = Cgb + Cpoly + Cmetal + Cj,min |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

= 0.52 fF + 2.42 fF + 0.90 fF + 4.71 fF = 8.55 fF |

|

|||||||||||||||||||||||||||||||||||||||

D Q |

|

|

|

|

= C |

|

|

|

V - |

VDD |

ö |

|

|

= 8.55 fF (3.68 V - 2.5 V) = 10.09 fC |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

critical,min |

|

|

x,min è |

max |

|

|

2 |

ø |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

t hold = |

Qcritical,min |

= 11.87ms |

|

|

|

|

||

Kenneth R. Laker, University of Pennsylvania |

|

Ileakage,max |

|

|

|

|

|

|

|

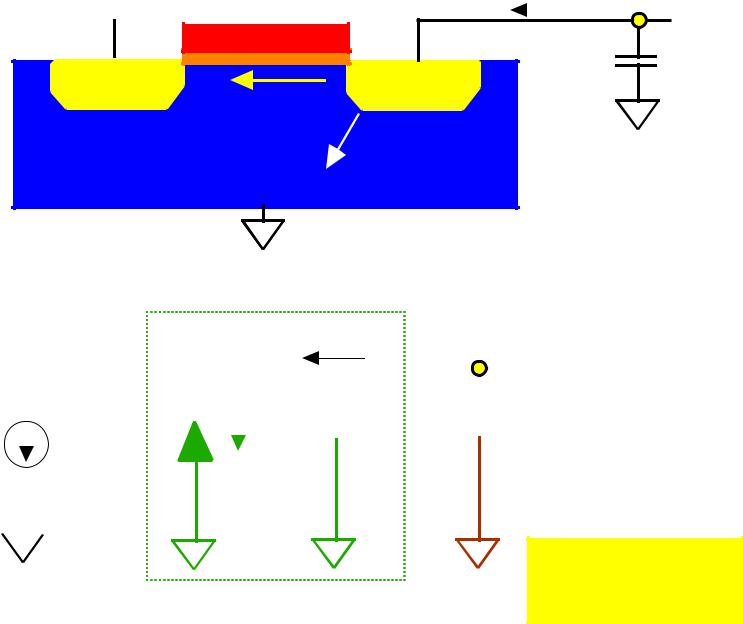

VOLTAGE BOOTSTRAPPING |

20 |

|

Useful dynamic circuit technique for ovecoming threshold voltage drops when nMOS enhancement pass transistors operate in SAT.

|

|

|

|

|

|

|

|

VDD |

|

Vin = 0, VDS2 = VDD - Vout > Vx - Vout - VT2 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

=> M1OFF, M2 SAT |

|||

Vx ≤ VDD |

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

M2 |

|

|

|

|

Vout |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

Vout(max) = Vx - VT2(Vout) |

|

||||||||

Vin = 0 |

|

|

|

|

|

|

|

|

|

|

|

Cout |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

M1 |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

MUST INCREASE VX |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vx |

M3 |

D |

|

|

|

|

S |

|

||

|

|

|

|

|

|

|

BOOTSTRAP: |

|

CS |

Cboot |

|

M2 |

|

+ VT2(Vout) |

|

|

Vout |

|||

BOOST Vx > VDD |

|

S |

||||

|

|

|

|

|||

|

|

|

Vin |

|

D |

|

|

|

|

|

M1 |

Cout |

|

|

|

|

|

|

|

|

Kenneth R. Laker, University of Pennsylvania |

|

|

|

S |

|

|

|

|

|

|

|

||