- •Глава 4: Память

- •При записи 1 – заряжаем,

- •Если постоянно читаем, то информация не теряется

- •2. Производительность

- •Для её роста повышают:

- •А также применяют

- •3. Синхронная (S) DRAM –

- ••строка целиком копируется в буфер

- •время доступа

- •4.Виды SDRAM

- •Схема

- •частота до 533 МГц

- •Схема

- •GDDR – ОЗУ для видеокарт

- •5. Спецификации DRAM

- •• Тайминги (времена задержек в тактах шины памяти)

- •Возможности

- ••напряжение (1.5–5 В)

- •• Регистровая – с мультиплексором между контроллером и банками – для роста объёма

- •6.Неисправности DRAM

- •Вентиляторы для модулей ОЗУ

- •Труднее всего устранить КЛ. Для полной защиты нужно десятки см свинца и т.

- •Случайный сбой раз в 10 лет

- •Нужны ли контроль чётности или коррекция (ECC)?

- •7.Классы качества

Глава 4: Память

§1 Оперативная память

1. Реализуется обычно на микросхемах DRAM =

Dynamic RAM, т.к. они имеют наилучшее сочетание

объёма информации

плотности записи

быстродействия

энергопотребления

цены (≈1 руб/МБ)

«Динамическая» – должна

постоянно работать:

При записи 1 – заряжаем,

0 – разряжаем

При чтении – всегда разряжаем

Если был 0, то 0 и останется 1, то заряжаем снова

Если постоянно читаем, то информация не теряется

Иначе, нужна периодическая

(раз в 0.01 с) регенерация – чтение каждой ячейки

2. Производительность

Это количество считанных или записанных байт в секунду

Н-р, DDR2 SDRAM: до 8 ГБ/с на канал при последовательном чтении нескольких байт, а

иначе до 1 ГБ/с

Для её роста повышают:

•быстродействие ячеек

•разрядность шины данных (до 256 бит!)

•объём и частоту буфера

(кэша)

• количество независимых банков (матриц): в одних идут

фазы чтения-записи, в других

– фаза восстановления

А также применяют

•конвейер – цикл обработки

•расслоение памяти – сохранение последовательных слов в разных модулях

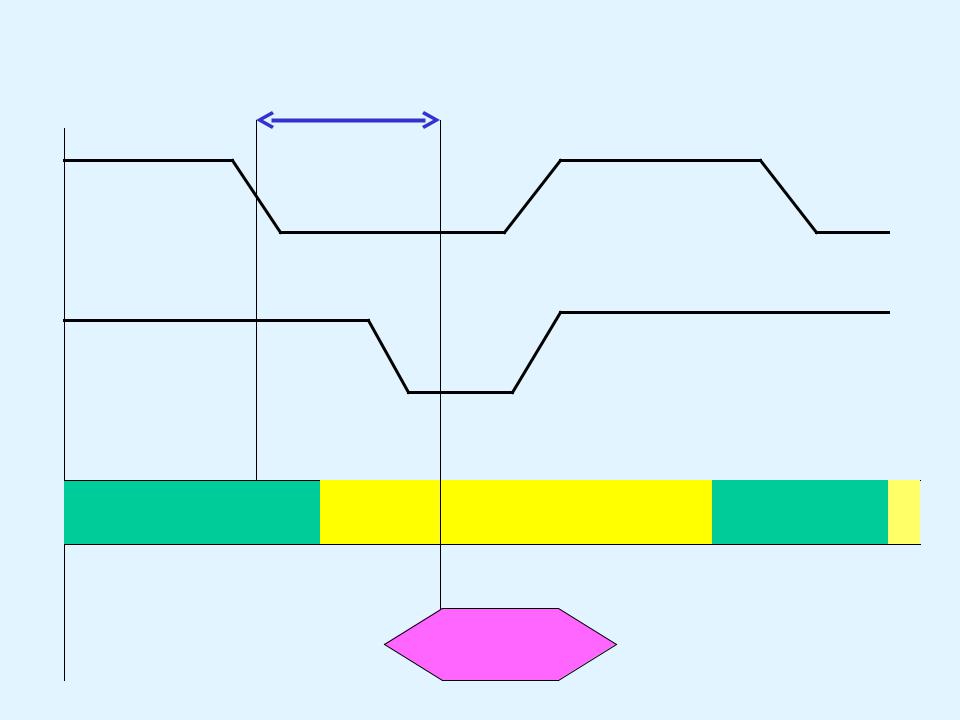

3. Синхронная (S) DRAM –

с конвейером

Контроллер памяти (в чипсете или ЦП) циклично выдаёт:

•номер чипа (CS# – Chip Select)

•номер банка (BA# – Bank Active)

•номер строки

•RAS# – Row Access Strobe – сигнал,

подтверждающий выставление номера строки на шину адреса

•строка целиком копируется в буфер

•номер столбца

•CAS#

•разрешение чтения или записи

•чтение ячейки из буфера

•закрытие строки (Precharge)

время доступа |

|

|

RAS# |

|

|

CAS# |

|

|

row |

column |

row |

|

data |

|