3_semestr / МУМК по Схемотехника цифр устройств / Контр.работа 2 Цифровые устройства

.doc

ЦИФРОВЫЕ УСТРОЙСТВА

Составители: Паутов Валентин Иванович

Секисов Юрий Николаевич

Федеральное агентство по образованию

ГОУ ВПО "Уральский государственный технический университет – УПИ"

Радиотехнический институт – РТФ

ЦИФРОВЫЕ УСТРОЙСТВА

Методические указания

для выполнения контрольного задания № 2

по курсу ‘Электроника’ для студентов всех

форм обучения специальности 210100-

Управление и информатика в технических системах

Екатеринбург 2005

УДК 621.38

Составители: В.И.Паутов, Ю.Н. Секисов,

Научный редактор доц., канд. техн. наук

В.В. Муханов

ЦЫФРОВЫЕ УСТРОЙСТВА: Методические указания для

выполнения контрольного задания № 2 по курсу ‘Электроника’ / В.И. Паутов, Ю.Н.Секисов.

Рассмотрены вопросы синтеза цифрового устройства для преобразования линейной функции в цифровой код с последующей передачей его в линию связи. Рассмотрен пример синтеза подобного преобразователя, приведены указания по выполнению контрольного задания.

Библиогр.: 11 назв. Рис. 11. Табл. 5.

Подготовлено кафедрой

Автоматика и управление в технических системах

© ГОУ ВПО "Уральский государственный

технический университет – УПИ", 2005

Вид титульного листа

"Уральский государственный технический университет – УПИ"

Кафедра автоматика и управление в технических системах

ПРЕОБРАЗОВАТЕЛЬ КОДА

Домашнее задание № 2

по курсу Электроника

Вариант № 28

Преподаватель

доц. к.т.н. В.И.Паутов

Студент

группа Р-34011 И.В.Журавлев

Дата

Екатеринбург 2005

По умолчанию предполагается, что входная функция в аналоговом виде поступает на преобразователь "аналог–код" – АЦП. На его выхо-

де формируется четырехразрядный код, который и используется в разрабатываемом преобразователе. Выходы АЦП соединить с входами преобразователя.

На чертеже текстом указывается номера выводов микросхем, на которые подается напряжение питания +5 вольт и – 5 вольт. Напряжение – 5 вольт, как правило, подключается к общей шине схемы.

В конце пояснительной записки в виде приложения приводится перечень элементов схемы электрической принципиальной. Этот перечень можно поместить также на самой схеме над штампом.

В данных указаниях приведены примеры использования микросхем серии 155. При разработке преобразователя можно использовать и другие серии 551, 553, а также микросхемы МОП и КМОП серий.

Ссылки на литературу в тексте оформляются следующим образом [2]. [2] – позиция 2 в библиографическом списке.

5. БИБЛИОГРАФИЧЕСКИЙ СПИСОК

-

Аналоговые и цифровые интегральные микросхемы /Под ред. С.В.Якубовского. М.: Радио и связь, 1984.

-

Гусев В.Г., Гусев Ю.М. Электроника. М.: Высшая школа, 1990.

-

Скаржепа В.А., Луценко А.Н. Электроника и микросхемотехника. Киев: Высш. Шк., 1989.

-

Расчет электронных схем: примеры и задачи. /Г.И. Изъюрова, Г.А. Королев, В.А. Терехов и др./ М.: Высш.шк., 1987.

-

Справочник по интегральным микросхемам / Под ред.

Б.В. Тарабина. М.: Радио и связь. 1983.

6. Стандарт предприятия. СТП УГТУ 1–96. Екатеринбург: УГТУ-УПИ. 1969.

7. Щило В.И. Популярные цифровые микросхемы. М.: Радио и связь. 1981.

8. Применение ИМС в электронной вычислительной технике: Справочник. / Под ред. Б.Н. Файзулаева. М.: Радио и связь. 1984.

-

Мокрецов В.П. Комбинационные схемы в МП системах: Учебное пособие. Свердловск: УПИ. 1989.

-

Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб.пособие. СПб.: Политехника, 1996.

-

Прянишников В.А. Электроника: Курс лекций. СПб.: КОРОНА принт, 1998.

18

-

КОМБИНАЦИОННЫЕ УСТРОЙСТВА

Устройства, оперирующие с двоичной (дискретной) информацией, подразделяются на два класса: комбинационные и последовательностные [2].

Комбинационные устройства (КУ) или комбинационные схемы характеризуются отсутствием в своем составе элементов памяти. Сигналы на их выходах в любой момент времени однозначно определяются сочетанием сигналов на входах и не зависят от предыдущего состояния. Схемными признаками таких устройств является отсутствие цепей обратной связи с выхода на вход. К КУ относятся сумматоры, дешифраторы, преобразователи кодов, мультиплексоры, цифровые компараторы и т.д. [1].

Сумматоры Сумматоры (обозначаются SM) представляют собой функциональные цифровые устройства, выполняющие операцию сложения двоичных чисел. В цифровой технике суммирование осуществляется в двоичном коде или, реже, в двоично-десятичном. По характеру действия сумматоры подразделяются на комбинационные и накопительные. В свою очередь каждый из сумматоров, оперирующий с многоразрядными числами, в зависимости от способа их сложения может быть отнесен к последовательному или параллельному типу. Как последовательные так и параллельные сумматоры строятся на основе одноразрядных суммирующих схем. Простейшей схемой является полусумматор. Примером сумматора двух четырехразрядных двоичных чисел может быть микросхема К155ИМ2.

Дешифраторы Дешифратор (DC) – комбинационное устройство с несколькими входами и выходами, у которого двоичным комбинациям входных сигналов соответствует активное состояние одного из выходов.

Используется три структуры дешифраторов: матричная, каскадная и пирамидальная.

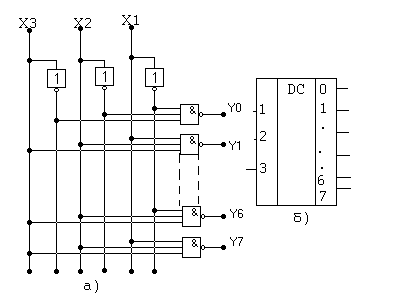

Матричные дешифраторы состоят из 2n логических схем совпадения &, каждая из которых имеет n входов. На входы подаются все возможные комбинации двоичного дешифрируемого числа Х. Пример матричного дешифратора 3Х8 приведен на рис. 1. Из схемы видно, что для преобразования трехразрядного кода необходимо использовать логические элементы & с тремя входами.

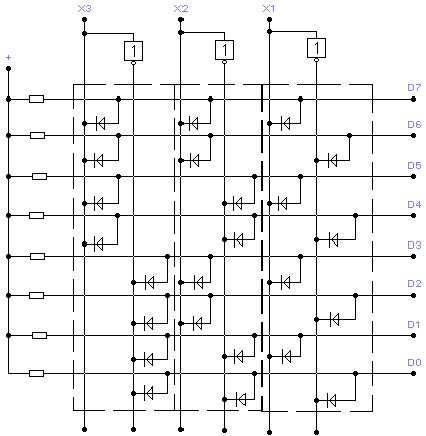

При значительной разрядности преобразуемого кода предпочтительней использование диодной логики. Пример такого дешифратора

3

Рис.1. Матричный дешифратор 3Х8: состав а), условное обозначение б)

приведен на рис. 2. Для увеличения разрядности такой дешифратор можно наращивать. На рис. 2 пунктиром обведена типовая ячейка. Так, дешифратор 2Х4 можно построить на основе дух таких схем, дешифратор 3Х8 – на основе трех схем и т.д. [2].

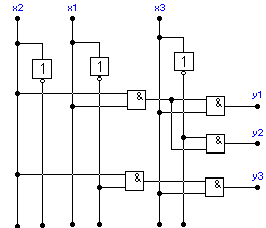

Пирамидальные дешифраторы отличаются тем, что каждая конституента единицы формируется как конъюнкция одной из конституент предыдущего каскада и одного из разрядов входного кода, еще не использовавшегося для формирования конституент. Принцип построения пирамидального дешифратора иллюстрируется на рис.3.

Из схемы видно, что в этом случае можно использовать логические элементы на два входа [4].

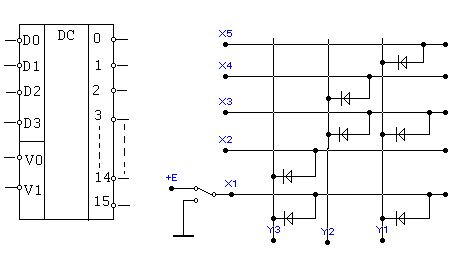

Дешифраторы имеются в составе нескольких серий ТТЛ. В качестве примера на рис. 4 приведено условное обозначение микросхемы дешифратора 4Х16 типа К155ИД3. Если на обоих входах V разрешения устанавливается 0 V0 = V1 = 0, то микросхема работает как дешифратор.

Команда V0 = V1 = 1 устанавливает высокий потенциал – логическую единицу – на всех выходах дешифратора независимо от состояния входов.

4

Можно использовать специальную микросхему – шинный формирователь, например, К155ЛЕ2.

В качестве генератора тактовых импульсов следует использовать любой генератор в интегральном исполнении, например, 155ГГ1.

Данное задание можно выполнить на базе микроконтроллера. В этом случае в отчете следует представить программу преобразования непрерывной функции в код, увеличив число точек отсчета вдвое, программу управления входным выходным портами. На принципиальной схеме представить микроконтроллер с указанием всех задействованных выходов, преобразователь параллельного кода в последовательный, линейный формирователь. Часть этих функций можно осуществить программным способом. Принципиальная схема должна сопровождаться описанием ее работы, временными диаграммами.

4. ОФОРМЛЕНИЕ РАБОТЫ

В отчете необходимо представить:

– задание на проектирование преобразователя с указанием номера варианта,

– таблицы преобразования,

– таблицу функционирования шифратора,

– принципиальную схему преобразователя, выполненную на формате А3 с соблюдением требований оформления электрических схем [6],

– описание работы принципиальной схемы со ссылками на временную диаграмму,

– временная диаграмма работы преобразователя,

– заключение о проделанной работе,

– список литературы, в котором указываются только те источники, которые использовались в работе.

Для черчения принципиальной схемы можно воспользоваться программой "Компас".

V/#

В

V/#

В

В

ход

ы

ход

ы

А

х

А

х

о

о

д

Рис.11. Обозначение аналого –

цифрового преобразователя

17

Таблица 4

|

Входная функция |

||||

|

1 |

2 |

3 |

4 |

5 |

|

Х |

πх |

Sinπx |

(24 – 1)*Sinπx |

(24 – 1)*Sinπx |

|

0 |

0 |

0 |

0 |

0000 |

|

0,1 |

9 |

0,16 |

2,5 |

0011 |

|

0,2 |

18 |

0,31 |

4,65 |

0110 |

|

0,3 |

27 |

0,45 |

6,75 |

0111 |

|

0,4 |

36 |

0,59 |

8,85 |

1011 |

|

0,5 |

45 |

0,71 |

10,7 |

1100 |

|

0,6 |

54 |

0,81 |

12,2 |

1101 |

|

0,7 |

63 |

0,89 |

13,4 |

1110 |

|

0,8 |

72 |

0,95 |

14,3 |

1110 |

|

0,9 |

81 |

0,99 |

14,8 |

1111 |

|

1,0 |

90 |

1,0 |

15 |

1111 |

Таблица 5

|

Выходная функция |

||||

|

1 |

2 |

3 |

4 |

5 |

|

Х |

πх |

Cosπx |

(25– 1) Сosπx |

(25 – 1) Cosπx |

|

0 |

0 |

1.0 |

31 |

11111 |

|

0,1 |

9 |

0,98 |

30,4 |

11110 |

|

0,2 |

18 |

0,95 |

29,7 |

11110 |

|

0,3 |

27 |

0,88 |

27,4 |

11011 |

|

0,4 |

36 |

0,80 |

24,8 |

11001 |

|

0,5 |

45 |

0,71 |

22,0 |

10110 |

|

0,6 |

54 |

0,57 |

17,7 |

10010 |

|

0,7 |

63 |

0,41 |

13,7 |

01110 |

|

0,8 |

72 |

0,29 |

9,0 |

01001 |

|

0,9 |

81 |

0,14 |

4,3 |

00100 |

|

1,0 |

90 |

00 |

00 |

00000 |

Можно использовать логический элемент с открытым коллектором, например, К155ЛА8 [10]. В этом случае соединяют параллельно два элемента. К их выходу также подключается резистор величиной 50 Ом. При использовании формирователя на транзисторе или на логическом элементе следует учитывать, что они являются инверторами в то время как в канале импульсы должны быть положительной полярности.

16

Рис.2. Матричный дешифратор на диодной логике

Данные микросхемы позволяют наращивание разрядности преобразуемых кодов.

Шифраторы Шифратором (CD) называется комбинационное устройство, преобразующее унитарный код, подаваемый на входные шины, в соответствующий двоичный код на выходе [4].

Рассмотрим в качестве примера синтез шифратора с пятью входами, преобразующего унитарный код в двоичный. Фрагмент таблицы истинности этого шифратора приведен в таблице 1.

Уравнения, описывающие функции Y1, Y2, Y3 наиболее удобно представить в виде следующих уравнений комбинационной логики

Y1 = Х5+Х3+Х1; Y2 = Х4+Х3; Y3 = Х2 + Х1.

5

Рис.3. Структура пирамидального дешифратора

Рис.4. Условное обозначение Рис.5. Схема для иллюстрации рабо- микросхемы дешифратора ты шифратор 5Х3 на диодах

4Х16 типа К155ИД3

6

соединяются с пятью выходными шинами шифратора в

соответствии с полученными в результате выполнения пунктов 2 и 3 кодами выходной и входной функций. При том двоичный четырехразрядный код входной функции на каждом из наборов определяет номер выхода шифратора, а соответствующий ему двоичный пятиразрядный код – узлы соединения этой выходной шины с соответствующей разрядной выходной шиной шифратора. Соединения выходной шины дешифратора и выходных шин шифратора осуществляются с помощью диодов. Диоды ставятся только в тех разрядах, в которых код выходного пятиразрядного двоичного числа равен единице. Схема преобразователя кода для рассматриваемого примера строится аналогично преобразователю рис.6.

В случае, если одному и тому же входному коду соответствуют различные выходные коды, следует взять одно из значений выходного кода.

Преобразование параллельного кода в последовательный возможно с помощью регистра либо мультиплексора. В первом случае код записывается в регистр по команде параллельной записи. Затем регистр по команде переводится в режим сдвига. После этого на управляющий вход регистра подаются такты сдвига, под действием которых код сдвигается и в последовательном виде появляется на выходе старшего разряда. Регистр должен иметь разрядность не менее пяти. Например, К531ИР24 или два включенных последовательно регистра К155ИР1. Команды параллельной записи и сдвига, а также такты сдвига формируются специальным управляющим устройством, в которое входит генератор импульсов.

В случае использования мультиплексора параллельный код подается на его информационные входы (входы D рис.7). На адресные входы (входы А, В, С) подается двоичный код, формируемый, например, с помощью двоичного счетчика, запускаемого генератором тактов. Счетчик считает до пяти, после чего автоматически устанавливается в нулевое (исходное) состояние. При этом вырабатывается импульс команды параллельной загрузки кода в регистр.

В обоих случаях для согласования

преобразователя с каналом связи ставится

формирователь импульсов, имеющий

выходное сопротивление 50 или 100 Ом.

Формирователь подключается к выходу F

или F

мультиплексора (рис.7) или к выходу

старшего разряда регистра. В качестве

формирователя можно использовать

транзистор, работающий в режиме ключа,

в коллекторную цепь которого включается

резистор.

обоих случаях для согласования

преобразователя с каналом связи ставится

формирователь импульсов, имеющий

выходное сопротивление 50 или 100 Ом.

Формирователь подключается к выходу F

или F

мультиплексора (рис.7) или к выходу

старшего разряда регистра. В качестве

формирователя можно использовать

транзистор, работающий в режиме ключа,

в коллекторную цепь которого включается

резистор.

15

Таблица 3

|

№ вар. |

Входная функция |

Выходная функция |

№ вар. |

Входная функция |

Выходная функция |

|

1 |

sinπx |

X |

15 |

1 - sin2πx |

0.9X |

|

2 |

cosπx |

X |

16 |

1 - cos2πx |

X |

|

3 |

1- sinπx |

0.8X |

17 |

X*sinπx |

sinx |

|

4 |

1- cosπx |

0.8*X |

18 |

X*sinπx |

cosx |

|

5 |

sinπx |

X2 |

19 |

X*(1 – sinπx) |

X |

|

6 |

cosπx |

X2 |

20 |

X*(1 – cosπx) |

X |

|

7 |

1 – sinπx |

X2 |

21 |

X*(1 – sinπx)2 |

sinx |

|

8 |

1 – cosπx |

X2 |

22 |

X*(1 – cosπx)2 |

cosx |

|

9 |

(1 – sinπx)2 |

0.5X |

23 |

X* |

X |

|

10 |

(1 – cosπx)2 |

X |

24 |

X* |

X |

|

11 |

|

X |

25 |

X* |

sinx |

|

12 |

|

X |

26 |

X* |

cosx |

|

13 |

sin2πx |

X |

27 |

1- Xsinπx |

1-x cosx |

|

14 |

cos2πx |

X |

28 |

sinπx |

cosπx |

Полученные данные переводят в двоичный четырехразрядный код. Для этого каждое из полученных дискретных значений функции умножают на число (24 – 1), результат округляют до ближайшего целого десятичного числа, которое и записывают в двоичном четырехразрядном коде. Результаты сводятся в таблицу. В качестве примера рассмотрен вариант 28 таблица 4. В первой строке указаны значения Х, в строке 2 – πx, в строке 3 – sinπx в десятичном коде, в строке 4 – (24 – 1) sinπx – значение преобразуемой функции sinπx в десятичном коде с учетом разрядности входного десятичного числа, в строке 5 – двоичный четырехразрядный код преобразуемой функции.

3.3. Определяются дискретные значения выходной функции при тех же значениях и по той же методике с учетом того, что выходная функция записывается в двоичном пятиразрядном коде. Результаты сводятся в таблицу. Для перевода функции cosπx в двоичный пятиразрядный код используется коэффициент (25 – 1).

3.4. Строится схема преобразователя кода. Для этого используется шифратор 4Х16. Выходные шины 0–15 которого с помощью диодов

14

Наиболее просто шифраторы реализуются на диодной логике, соединенной по схеме логическое ИЛИ. Так, для приведенного примера диодный шифратор должен иметь пять входных и три выходных шины. Каждая входная шина соединяется через диоды с выходными в соответствии с уравнениями или таблицей 1 рис.5. При появлении положительного потенциала на шине Х1 на выходе Y1 и Y3 также появляются высокие потенциалы, т.е. формируется код 101. При этом предполагается, что Х2=Х3=Х4=Х5=0.

Шифраторы, выполненные виде микросхем, преобразуют сигнал в виде унитарного кода, в котором активным является только один разряд в выходной параллельный двоичный код. Например, на клавиатуре нажимается клавиша с цифрой 9, а шифратор клавиатуры преобразует этот факт в виде двоичного кода 1001.

Таблица 1

|

Входы |

Выходы |

||||||

|

Х1 |

Х2 |

Х3 |

Х4 |

Х5 |

Y1 |

Y2 |

Y3 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

Преобразователи кодов Преобразователь (ПК, Х/Y) – комбинационные устройства, предназначенные для преобразования одного параллельного кода в другой тоже параллельный. Они используются для шифрации и дешифрации цифровых кодов и могут иметь n входов и к выходов К = 2n.

По назначению ПК делят на два типа: с невесовым и с весовым преобразованием кодов. В преобразователях первого типа отсутствует численная зависимость входного и выходного кодов, а имеется символьная взаимозависимость. Например, преобразование двоично-десятичного кода в код семисегментного индикатора десятичных цифр. Преобразователи второго типа используются как правило, для преобразования числовой информации, когда между числами входного и выходного кодов имеется заданная математическая зависимость [7, 8].

Преобразование n-элементного кода в к-элементный можно осуществить с предварительной шифрацией входного кода и без нее.

В первом случае сначала шифрируется n -элементный код и на

7

каждом из 2n выходах получается сигнал, соответствующий одной из входных кодовых комбинаций.

Затем каждый из выходных кодов кодируется в к-элементный код при помощи шифратора.

Рассмотрим в качестве примера преобразование трехэлементного кода в пятиэлементный, представленный в таблице 2.

Таблица 2

|

Трехэлементный код |

Пятиэлементный код |

||||||

|

Х3 |

Х2 |

Х1 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |