Варианты курсовых по Козлову / Kursovaya_rabota_17

.docxМИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ

РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение

высшего профессионального образования

«Чувашский государственный университет имени И. Н. Ульянова»

Электроэнергетический факультет

Кафедра «ТОЭ И РЗА»

КУРСОВАЯ РАБОТА

по учебной дисциплине

«МИКРОПРОЦЕССОРНЫЕ СРЕДСТВА УПРАВЛЕНИЯ»

Вариант 17

Выполнил: Студентка группы ЭЭ-21-08

Назарова З. В.

Руководитель проекта: к. т. н., доцент

Козлов В. Н.

Чебоксары 2012

Исходные данные для моделирования микропроцессорного устройства.

|

Вариант |

Адрес RA |

Адрес RB |

Адрес дискретных входов |

Тип логической функции |

Адрес результата логической функции Y |

Блокировка |

По какому условию |

|

17 |

2 |

3 |

4 |

Инверс.(RA+SA) + RB |

5 |

Чтения SА |

RА=7 |

Схема

модели микропроцессорного устройства.

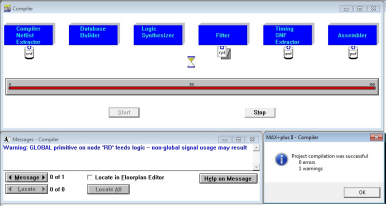

Процесс компиляции.

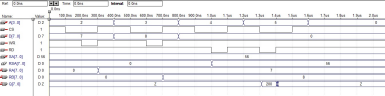

Расчеты.

Блокировка.

Ручной расчет.

RA=6=00000110 RB=8=00001000 SA=56=00111000

Y=Инверс.(RА+SA)+RB=Инверс.(00000110+00111000)+00001000=11001001=201 При блокировке: RA=7=00000111 RB=8=00001000 SA=56=00111000

Y=Инверс.(RА+SA)+RB=Инверс.(00000111+00111000)+00001000=11001000=200

Вывод: В данной курсовой работе мною была смоделирована схема работы микропроцессорного устройства с блокировкой чтения SA при RА=7. Совпадение ручного и машинного расчета показывает, что модель функционирует правильно.