- •Тема 1. Напiвпровiдниковi прилади

- •1.2. Провiднiсть напiвпровiдникiв

- •1.3. Електронно-дірковий перехід

- •1.4. Напівпровідникові діоди

- •1.5. Біполярні транзнстори

- •Між характеристичними та внутрішніми параметрами транзистора для кожної схеми вмикання існує певний зв’язок.

- •1.6. Польові транзнстори

- •Тема 2. Інтегральні мікросхеми

- •1.1. Планарна технологія

- •2.2. Основні терміни і визначення в мікроелектроніці

- •2.4. Напівпровідникові інтегральні мікросхеми

- •2.5. Тонкоплівкові гібридні інтегральні мікросхеми

- •Тепер можна оцінити питому ємність діелектрика із виразів

- •Тема з. Оптоелектронні елементи tа системи

- •3.1. Особливості оптоелектроніки

- •3.2. Джерела (випромінювачі) світла

- •3.3. Фотоприймачі

- •Загальний колекторний струм фототранзистора

- •3.4. Оптичні лінії зв'язку

- •3.5. Оптоелектронні індикатори

- •3.6. Оптрони

- •Mіkросхеmоtехhіка

- •Тема 4. Електронні підсилювачі

- •4.1. Класифікація та структурні схеми підсилювачів

- •Розглядаючи вхідне коло підсилювача з джерелом напруги (рис. 4.1, а), можемо записати

- •4.2. Осhоbhі характеристики підсилювачів

- •Для багатокаскадного підсилювача

- •4.3. Режим роботи підсилювального каскаду

- •4.4. Зворотний зв'язок у підсилювачах

- •Тема 5. Базові елементи лінійних інтегральних підсилювачів.

- •5.1. Особливості аналогової інтегральної схемотехніки

- •5.2. Методи забезпечення і стабілізація режиму роботи транзисторного каскаду підсилення

- •5.3. Елементарні каскади підсилення

- •5.4. Складений транзистор

- •5.5 Диференційні каскади підсилення

- •5.6. Вибіркові каскади підсилення

- •Тема 6. Операційні підсилювачі

- •6.1. Призначення та основні властивості операційних підсилювачів

- •6.2. Передавальні характеристики операційних підсилювачів

- •6.3. Сtруktурhі схеми операційних підсилювачів

- •6.4. Операційні підсилювачі загального призначення

- •6.5. Операційні підсилювачі окремого застосування

- •6.6. Найважливіші показники операційних підсилювачів

- •6.7. Інвертуюче, неінвертуюче та диференційне ввімкнення операційних підсилювачів

- •Вхідний і вихідний опори такої моделі в першому на6лиженні визначаються рівняннями

- •6.8. Розв'язуючі пристрої на стандартних операційних підсилювачах

- •Якщо до входу оп прикласти напругу в вигляді стрибка із сталою амплітудою Uд, то

- •Тема 7. Генератори гармонічних kоливань

- •7.1. Класифікація та ііризначення генераторів гармонічних коливань

- •7.2. Умови самозбудження автогенераtорів

- •Таким чином, щоб одержати стійкий автоколивальний процес з частотою коливань

- •7.5. Стабілізація частоти вихідних коливань в автогенераторах

- •Тема 8. Імпульсні пристрої на інтегральних mікросхеmах

- •8.1. Особливості імпульсного режиму електронних пристроїв

- •8.2. Ключовий режим роботи біполярних транзисторів

- •При цьому струм колектора в режимі насичення

- •8.3. Імпульсний режим роботи операційних підсилювачів. Компаратори

- •Скориставшись рівністю (8.11) та (8.12) для напруги гістерезисну, отримаємо

- •8.4. Диференціюючі та інтегруючі ланцюжки

- •8.1. Електронні ключі

- •8.6. Автоколивні мультивібратори

- •Період коливань мультивібратора симетричної схеми

- •Тривалість зрізу залежить від часу заряджання конденсатора

- •Частота слідування імпульсів

- •8.7. Загальмовані мультивібратори

- •Має низький негативний рівень, а напруга , що збігається з напругою на відкритому діоді vd1, майже дорівнює нулю.

- •8.8. Генератори лінійно–змінної напруги

- •Тема. 9. Цифрові елементи та пристрої

- •9.1. Загальна характеристика цифрових логічних інтегральних мікросхеm

- •9.2. Схеми цифрових логічних елементів

- •9.3. Тригери

8.2. Ключовий режим роботи біполярних транзисторів

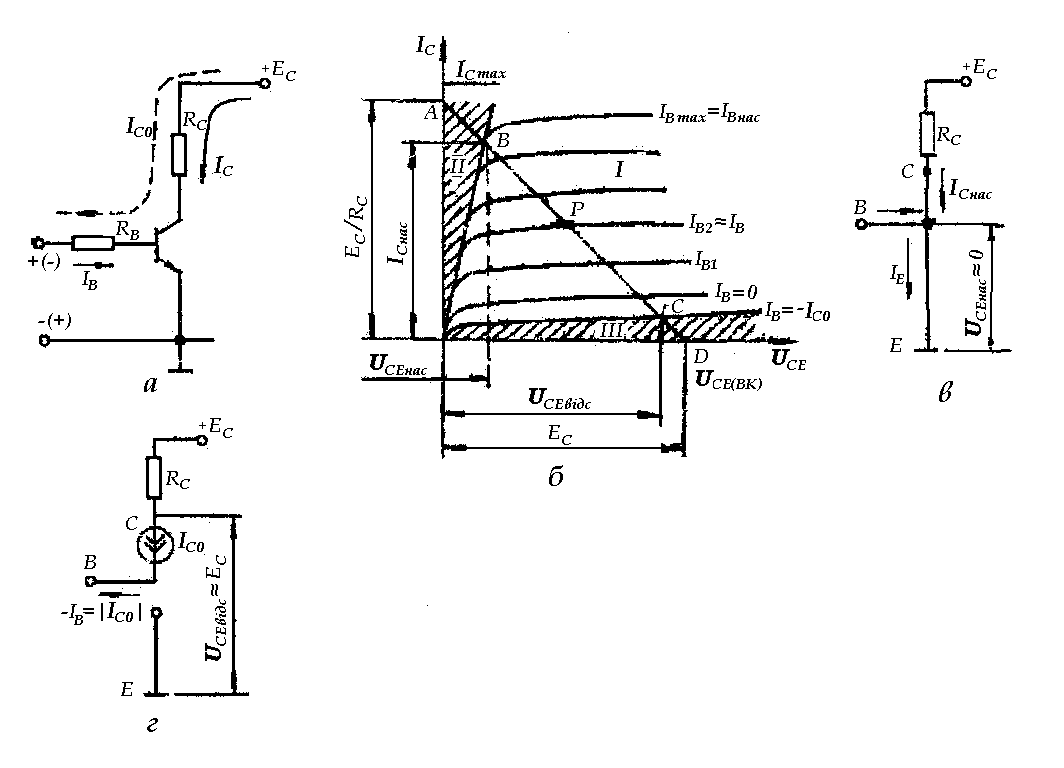

Основою усіх схем імпульсної техніки є ключова схема, яка являє собою транзисторний підсилювальний каскад, що працює у ключовому режимі. Транзистор у ключовій схемі (рис. 8.3, а) виконує функцію безконтактного ключа в послідовному колі з резистором RС та джерелом живлення ЕС. Якість такого ключа визначається здебільшого залишковою напругою на транзисторі в замкненому (відкритому) стані, а також залишковим струмом транзистора у вимкнутому (закритому) стані.

Аналіз процесів у схемі транзисторного ключа легко проводити графоаналітичним методом, скориставшись лінією аб навантаження постійним струмом (рис. 8.3, 6), збудованою на ряді статистичних характеристик транзистора при опорі навантаження R та напрузі джерела живлення ЕС. Ключова схема виконана на транзисторі за схемою із ЗЕ.

Рис.

8.3

Рис.

8.3

Якщо робоча точка р не виходить за межі ділянки BF навантажувальної прямої, то такий режим роботи транзистора навивають лінійним або підсилювальним. При цьому зі зміною вхідного (базового) струму пропорційно змінюється вихідний (колекторний) струм На рис. 8.3, б лінійний режим відзначений як активна область І. Якщо вхідний струм досягне ІВmах = ІВНАС (точка В на рис. 8.3, б),то подальше підвищення не призведе до зростання колекторного струму, який досягає струму насичення ІСНАС.

При цьому напруга на колекторі UСЕНАС невелика (звичайно кілька десятків мілівольт), отже, UСЕНАС << ЕC, Параметр ІВНАС називають струмом бази на межі насичення. У режимі насичення на вхід подається відкриваючий позитивний стрибок напруги Uвх(полярність по казана без дужок на рис. 8.3, а), емітерний та колекторний переходи транзистора зміщуються у прямому напрямі. Тому умова насичення транзистора, виражена через напругу, має вигляд

UВЕ > 0; UВС > 0, (8.1)

а транзистор можна зобразити у вигляді замкненого ключа (рис. 8.3, в). Зі схеми видно, що транзистор в режимі насичення можна розглядати як еквіпотенційну точку з однаковими потенціалами всіх електродів. Безперечно, в цьому випадку струми в транзисторі визначаються лише параметрами зовнішніх елементів схеми. Умовою насичення транзистора, яка виражена через струм, є нерівність

ІВ ≥ ІВНАС = ІСНАС /h21Е . (8.2)

При цьому струм колектора в режимі насичення

ІСНАС = (ЕС – |UСЕНАС |)/RС ≈ ЕС /RС (8.3)

визначається лише напругою джерела живлення та опором навантаження і не залежить від вибору транзистора. Струм бази в режимі насичення з урахуванням виразу (8.2) має вигляд

![]() (8.4)

(8.4)

Для кількісної оцінки глибини насичення використовують параметр, що називається ступенем насичення,

КНАС = ІВ /ІВНАС , (8.5)

звідки отримуємо умову насичення з урахуванням нерівності (8.2)

КНАС ≥ 1. (8.6)

Область насичення ІІ (рис. 8.3, б) розміщується зліва від некерованої ділянки статистичної колекторної характеристики. Для збереження нормального теплового режиму в транзисторі струм ІСНАС не повинен перевищувати максимально

допустимий струм колектора ІСmах

tф = τh21Е ln[KHАC /(КНАС –1)], (8.7)

τh21Е = 1/ωh21Е = 1/2πƒh2ІЕ – стала часу перехідного процесу в транзисторі з ЗЕ; ƒh2ІЕ – гранична частота підсилення транзистора. З формули випливає, що тривалість ввімкнення найменша тоді, коли найбільший ступінь насичення КНАС транзистора або чим більший відкриваючий струм бази ІВ. Область відсічки ІІІ (рис. 8.3, б) відповідає закритому стану транзистора, який можна зобразити схематично як розімкнений ключ (коло емітера вимкнуте) (рис. 8.3, г). Закритий стан транзистора досягається зміщенням емітерного та колекторного переходів у зворотному напрямі. Тому умову відсічки транзистора можна записати у вигляді

UВЕ ≤ 0; UВС ≤ 0, (8.8)

У режимі відсічки на вхід підсилювального каскаду подається закриваючий негативний стрибок напруги Uвх (на рис. 8.3, а полярність показана в дужках). Коли обидва переходи транзистора зміщені в зворотному напрямі, через них

протікають лише зворотні некеровані струми. При цьому в колекторному колі протікає струм ІС = ІС0, а в базовому – 1В = – ІС0 , змінюючи напрям. Струмом емітера нехтуємо. Напруга на колекторі закритого транзистора.

UСЕ відс = ЕС – ІС0RС. (8.9)

Виходячи з того, що ЕС >> ІС0RС, вважаємо, що UСЕ відс дорівнює напрузі джерела живлення.

Тривалість процесу вмикання транзистора (розімкнення ключа) значною мірою визначається часом розсмоктування надлишкових носіїв заряду в його базі. Коли концентрація надлишкових носіїв більша за глибину насичення транзисторів, то час розсмоктування

tр = τh21Е lnKHАC (8.10)

можна зменшити, знижуючи ступінь насичення транзистора.

Тривалість процесів вмикання та вимикання транзистора визначає швидкодію транзистора в ключовому режимі. Головною особливістю ключового режиму (режиму відсічки та насичення) є некерованість колекторного струму транзистора.