Основы радиосхемотехники / Учебник по САЭУ(2005) / САЭУ кн.1 / Гл.4-7

.doc

а знаменатель выражения (4.22) представить в виде:

F1(0)=1+2RЭS0/(1+2RЭg11)=1+S0/(g11+1/2RЭ) (4.22/)

Дифференциальный каскад, усиливая дифференциальный сигнал, должен значительно подавлять синфазную компоненту. Увеличение глубины обратной связи для подавления синфазного сигнала в ДК можно получить посредством выбора большой величины сопротивления резистора RЭ. Из (4.22/) следует, что при увеличении сопротивления RЭ глубина ОС стремиться не к бесконечно большой, а к предельной величине, определяемой выражением:F1(0,макс)=1+S0/g11=1+h21, где h21-коэффициент усиления тока транзистора в режиме короткого замыкания в выходной цепи. В то же время из (4.22) следует, что при фиксированной величине K0, увеличение RЭ может привести к заметному ослаблению синфазного сигнала во входной цепи, поскольку:

Lim αпос=0 при RЭ→∞. (4.22//)

Таким образом, ослабление синфазного сигнала в ДК, составляющее обычно величину 80-100 дБ, определяется не только глубиной последовательной ООС по току, но и значительным ослаблением этого сигнала во входной цепи, вызываемым согласно (4.22//) уменьшением коэффициента αпос :

![]() . (4.22///)

. (4.22///)

Уровень синфазного сигнала дополнительно уменьшается и ослаблением его в выходной цепи каскада, поскольку:

ZВХ(ос)=Z22=2RЭ.

Если учесть это дополнительное ослабление синфазного сигнала в выходной цепи, то выражение (4.22///) должно быть записано в виде:

Номинал резистора RЭ

для получения значительного ослабления

синфазного сигнала при этом должен быть

порядка нескольких мегом. Для получения

столь больших номиналов в ДК вместо

пассивных резисторов используют

специальные схемы, обладающие малым

сопротивлением постоянному току и

большим дифференциальным сопротивлением

для переменной составляющей. Подробнее

эти вопросы рассмотрены в следующей

главе. Детальное исследование также

показывает, что при больших номиналах

RЭ существует

конечная величина

![]() ,

при которой синфазный сигнал в выходной

цепи полностью исчезает, а при дальнейшем

увеличении сопротивления RЭ

вновь появляется. Это происходит за

счет явления просачивания синфазного

сигнала из входной цепи каскада в его

выходную цепь по четырехполюснику

обратной связи. При этом учитывается,

что каскад изменяет полярность(фазу)

выходного сигнала по отношению ко

входному . Можно показать, что:

,

при которой синфазный сигнал в выходной

цепи полностью исчезает, а при дальнейшем

увеличении сопротивления RЭ

вновь появляется. Это происходит за

счет явления просачивания синфазного

сигнала из входной цепи каскада в его

выходную цепь по четырехполюснику

обратной связи. При этом учитывается,

что каскад изменяет полярность(фазу)

выходного сигнала по отношению ко

входному . Можно показать, что:

![]() , (4.22////)

, (4.22////)

где RI=1/g22- дифференциальное сопротивление выходной цепи транзистора в рабочей точке, μ=S0RI.- максимальный коэффициент усиления напряжения выходной цепи каскада в режиме холостого хода.

4.4.2. Усиление дифференциального сигнала

Принципиальная схема ДК при возбуждении

его дифференциальным сигналом изображена

на рис.4.31а. Нетрудно убедиться, что

приращение тока

![]() в сопротивлении RЭ,

вызванное левым источником сигнала Ug,

будет равно по величине и противоположно

приращению тока

в сопротивлении RЭ,

вызванное левым источником сигнала Ug,

будет равно по величине и противоположно

приращению тока

![]() ,

вызванного правым источником сигнала,

так что

,

вызванного правым источником сигнала,

так что

![]() ,

поэтому

,

поэтому

![]() .Таким

образом, при возбуждении ДК дифференциальным

сигналом, приращение напряжения на

резисторе RЭ

схемы рис. 4.31а оказывается равным

нулю- «виртуальный нуль». В этом случае

резистор RЭ из

схемы рис. 4.31а может быть исключен

и принципиальная схема ДК будет выглядеть

так, как показано на рис. 4.31б. Из

последнего рисунка следует, что при

усилении дифференциального сигнала

плечи каскада также работают независимо,

причем сигнал Ug

усиливается каждым резисторным каскадом

с включением транзисторов с общим

эмиттером.

.Таким

образом, при возбуждении ДК дифференциальным

сигналом, приращение напряжения на

резисторе RЭ

схемы рис. 4.31а оказывается равным

нулю- «виртуальный нуль». В этом случае

резистор RЭ из

схемы рис. 4.31а может быть исключен

и принципиальная схема ДК будет выглядеть

так, как показано на рис. 4.31б. Из

последнего рисунка следует, что при

усилении дифференциального сигнала

плечи каскада также работают независимо,

причем сигнал Ug

усиливается каждым резисторным каскадом

с включением транзисторов с общим

эмиттером.

Рис.4.31

а Рис.4.31

б

Тогда комплексный коэффициент передачи напряжения левого плеча: U2(g,a)/Ug=-K0/(1+jωτВ), а правого плеча:

U2(g,б)/Ug=+K0/(1+jωτВ),

где K0=S0/(gi+gK), τВ=τ+С/КБ/(gi+gk).

Приведенные выражения справедливы во всей частотной области (нижних, средних и верхних частот).Поскольку:

Ug=[U1(a)-U1(б)]/2 ,

то усиление левого плеча ДК будет:

U2(g,a)/[U1(a)-U1(б)]= -K0/2 (1+jωτВ),

а правого плеча:

![]()

На симметричном выходе сигналы удваиваются и поэтому:

![]()

.

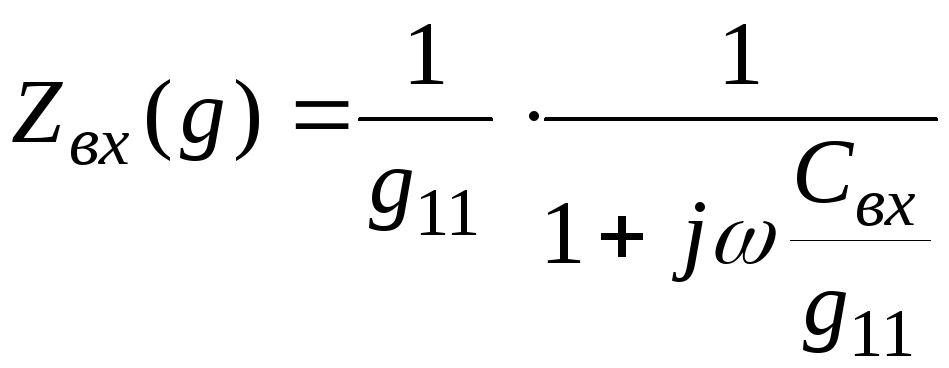

Входное сопротивление.

Поскольку при усилении каскадом дифференциальных cигналов обратная связь отсутствует, то входное сопротивление каскада для сигнала Ug будет такое же, как и в обычном резисторном каскаде, с учетом рис.4.31б запишем:

,

,

где

![]() - входная динамическая ёмкость каскада

без обратной связи. Вследствие глубокой

ООС для синфазного сигнала входное

сопротивление ДК этому сигналу очень

велико, оно записывается в виде:

- входная динамическая ёмкость каскада

без обратной связи. Вследствие глубокой

ООС для синфазного сигнала входное

сопротивление ДК этому сигналу очень

велико, оно записывается в виде:

![]() .

.

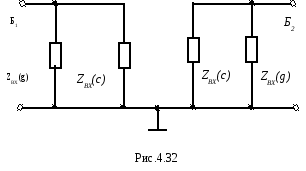

Учитывая принципиальную схему ДК, эквивалентную схему для входного сопротивления каскада с учетом как синфазного, так и дифференциального сигнала можно изобразить так, как представлено на рис.4.32, где Б1 и Б2 – базовые выводы транзисторовVT1,VT2.