Лабораторные работы / Отчет Лабораторная работа

.docxФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ АВТОНОМНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

МОСКОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра Автоматика и управление

направление подготовки

«Информационные системы и технологии»

Дисциплина: Программируемые логические интегральные схемы

ЛАБОРАТОРНАЯ РАБОТА № 3

Темы: Разработка арифметико-логического устройства

Выполнил: студент группы ____________

____ ______

(Фамилия И.О.)

Дата, подпись ____

(Дата) (Подпись)

Проверил: ___________

(Фамилия И.О., степень, звание) (Оценка)

Дата, подпись ________________ ___________

Москва

2022

Цель работы:

Необходимо разработать и промоделировать работу 4-разрядного АЛУ с последовательной и параллельной организацией арифметического переноса. За схемотехническую основу предлагается взять классическую структуру АЛУ.

Выполнение:

Был создан новый проект с данными настройками:

Device Family: Cyclone II, Package: FBGA, Pin Count: 484, Speed Grade: 7, Available Devices: EP2C20F484C7.

Далее была произведена разработка Verilog-описания сумматора SM с последовательной организацией переноса.

Следующим этапом были получены входные сигналы для сумматора SM в симуляторе.

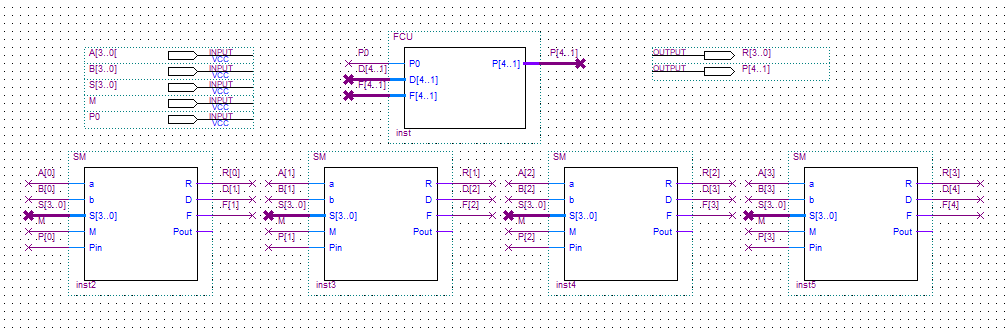

Далее сборка схемы АЛУ с последовательным переносом.

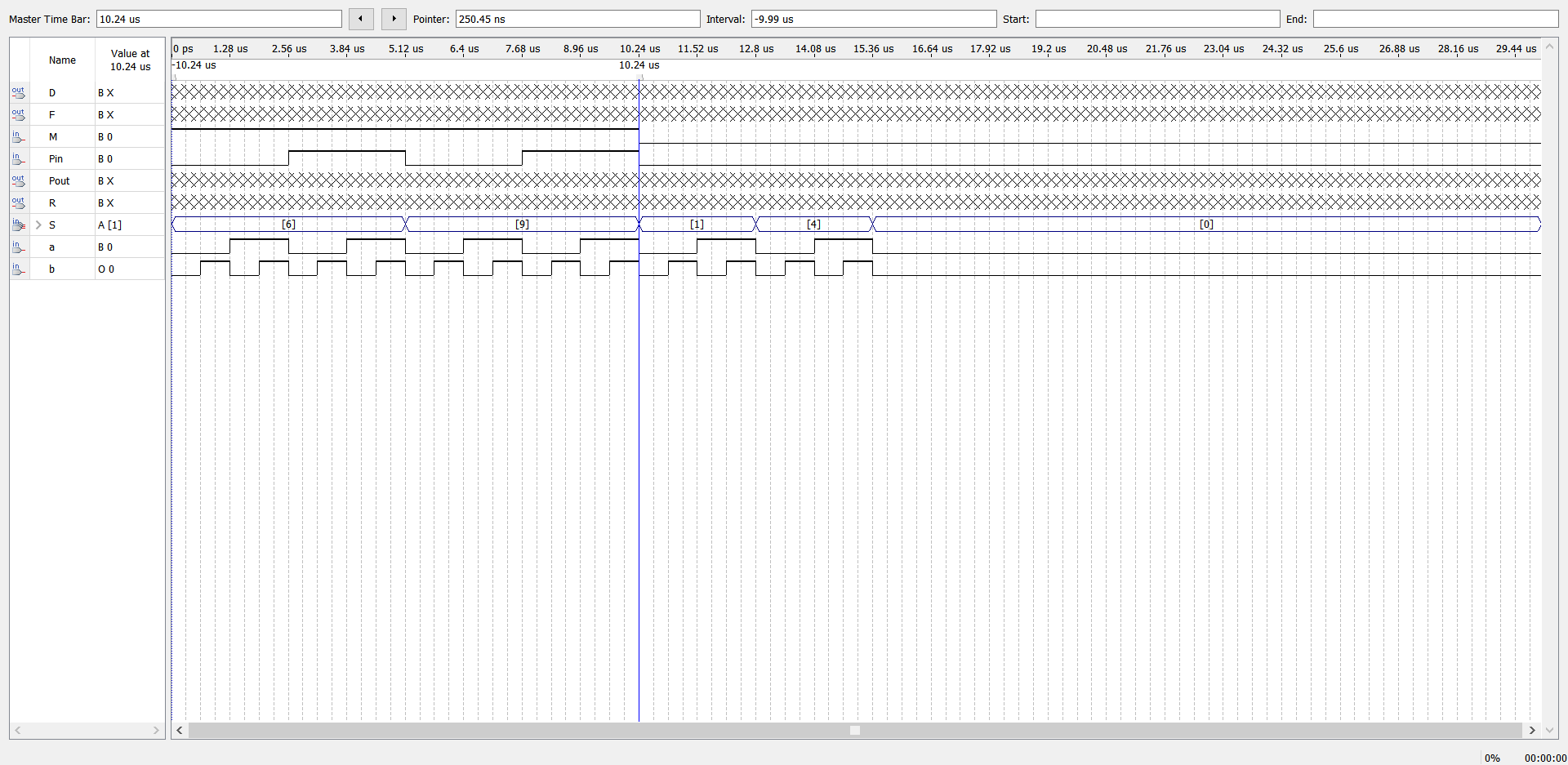

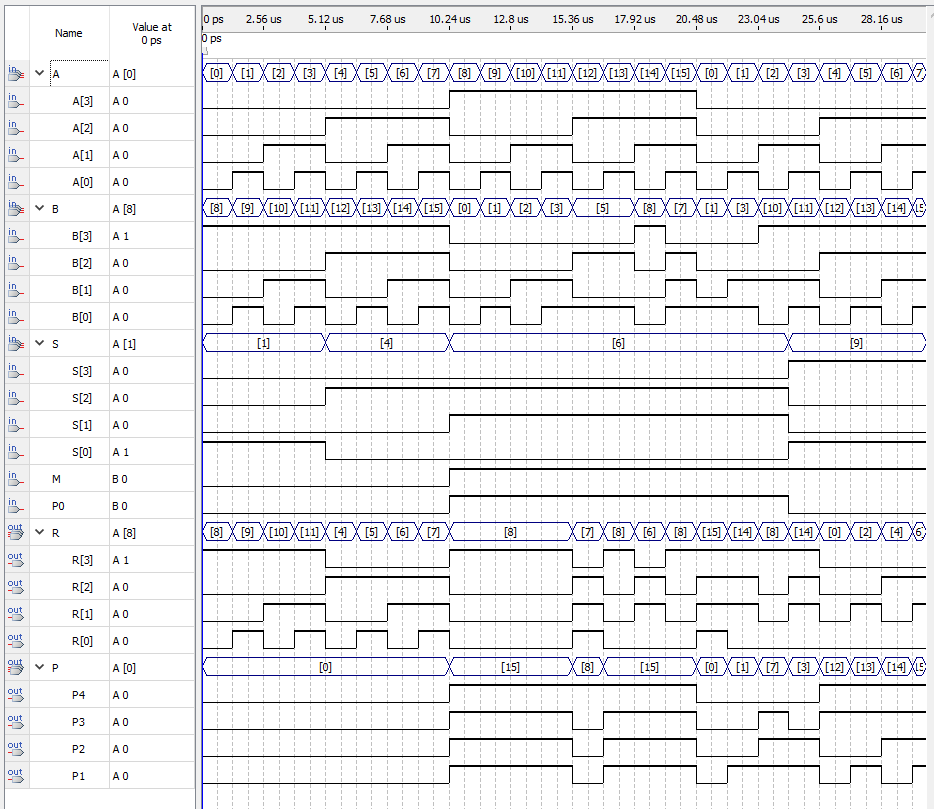

Входные сигналы для АЛУ с последовательным переносом в симуляторе.

Проверка работы АЛУ с последовательным переносом в симуляторе.

Для разработки HDL-описания СУП, сборка схемы АЛУ с параллельным переносом необходимо так же создать новый проект.

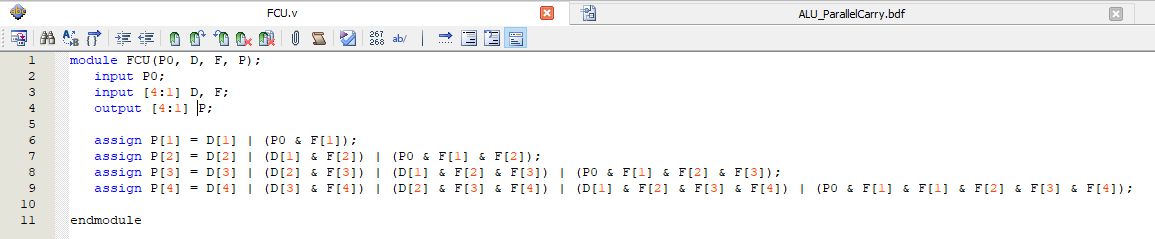

Разработка Verilog-описания сумматора SM с параллельной организацией переноса.

Сборка схемы АЛУ с параллельным переносом.

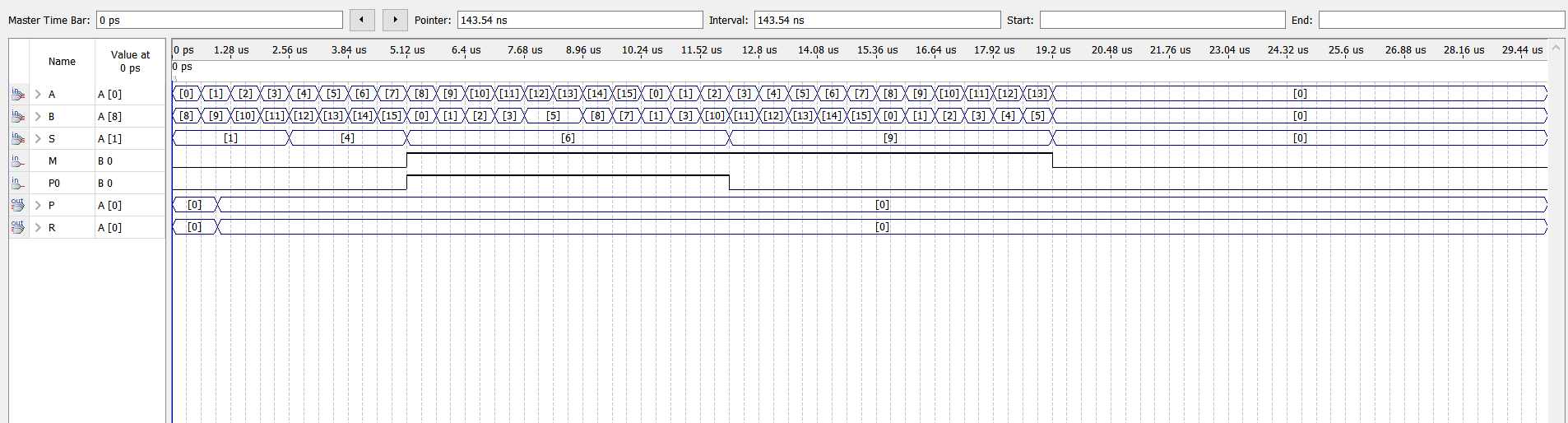

Проверка работы АЛУ с параллельным переносом в симуляторе.

Вывод:

В данной работе был составлен АЛУ с последовательной и параллельной организацией арифметического переноса. Стоит отметить, что схема с последовательным переносом используется, когда не требуется высокое быстродействие, но предъявляются жесткие требования к аппаратным затратам, а схема с параллельным переносом обеспечивает более высокое быстродействие.